### India Not Rated

# **Technology - Others**

### Semiconductors deep dive: India & the world

- Global semicon revenue to soar to US\$700bn in FY25F; TSMC commanding 90% of adv. chip output & India FY24 electronics exports at 6.3% of total trade.

- India semiconductor mission with Rs7,60,000m outlay led to Rs1.56tr investments, cutting the US\$60bn electronics import gap via new fabs & ATMP.

- India's first Tata-PSMC fab in Dholera costing Rs915bn will produce 50,000 wafers monthly by FY26F alongside four ATMP projects approved across India.

### From electronics assembly to climbing the semicon value chain

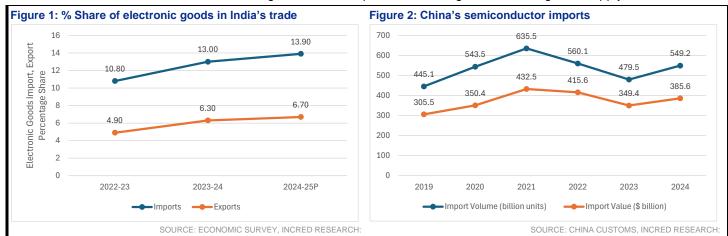

India is undergoing a structural shift in its digital and industrial base, led by policies like the **India Semiconductor Mission (ISM)** and **IndiaAl Mission**. The government's initial thrust came through various schemes under the **National Policy on Electronics (NPE) 2019**, which positioned India as a major hub for **electronics assembly** — particularly in smartphones and consumer devices. While local **value addition in electronics manufacturing currently stands at 15–20%**, the target is to raise this to **35% or more** in the coming years. Building on this momentum, the focus is now shifting towards **higher value-adding segments** in the semiconductor chain which include **ATMP**, **wafer fabrication**, and **chip design**. With electronics imports rising (10.8% to 13.9% of total imports between FY22–FY24), achieving end-to-end capability is now central to India's push for technology sovereignty.

### Building from the ground up

India's early gains lie in ATMP and mature-node fabs — a pragmatic entry point. But semiconductors are a highly cyclical, capital and R&D-heavy sector. Countries like Taiwan and South Korea succeeded because of sustained and evolving government support, not one-time interventions. India has shown flexibility by updating schemes based on feedback — but staying globally competitive in the face of US and China-scale subsidies will demand continued reinvention and deep and continuous execution support.

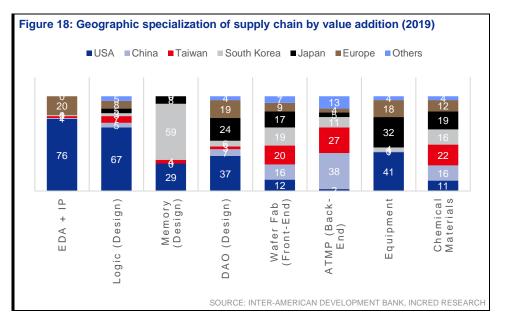

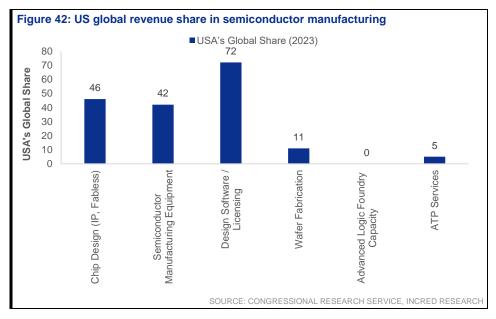

### Winning with design and AI, losing on value

**Design contributes nearly 50% value addition to the entire semiconductor value chain**, and India holds **19% of the global design talent**. Yet, most of the value accrues to foreign companies that retain intellectual property or IP ownership, limiting domestic value capture. A similar gap exists in AI — India hosts about **16% of the global AI talent pool** but lacks core AI infrastructure and proprietary models. To address this, the **Design-Linked Incentive (DLI) Scheme** and the **IndiaAI Mission** aim to promote indigenous IP, domestic startups, and stronger integration between chip design and AI innovation. With rising demand for AI chips, particularly in edge and accelerator segments, capturing more of this value is key to positioning India as a global technology leader — not just a talent provider.

### Gaps in execution persist

While India aims to build a full-stack semiconductor ecosystem, execution has been uneven across certain high-impact segments. Although the government has shown strong intent to catalyze the entire value chain, it has struggled to attract viable investment under its flagship Display Fab Scheme as well as the Compound Semiconductor and ATMP Scheme, both part of the India Semiconductor Mission. This reflects the need for further policy refinement, improved risk-sharing mechanisms, and greater alignment with private sector expectations to convert strategic intent into operational momentum.

Research Analyst(s)

Shubham DALIA T (91) 02241611544 E shubham.dalia@incredresearch.com

# The heart of modern tech – Understanding semiconductors and their evolution

### What are semiconductors? >

Semiconductors are materials whose electrical conductivity lies between that of conductors and insulators. Their unique properties enable control over electrical signals, making them the foundation of modern electronics. Semiconductors are used to build components like transistors, diodes and integrated circuits (ICs) which power everything from smartphones and laptops to satellites and missiles and AI accelerators.

### The strategic importance of semiconductors >

Semiconductors are the "brains" behind virtually every modern machine. As countries across the world digitize and militarize simultaneously, chips have evolved from simple computing enablers to strategic geopolitical assets. This transformation is underscored by a few key dynamics:

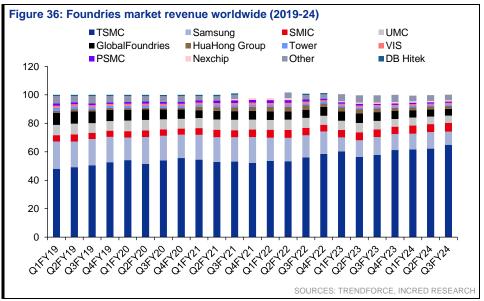

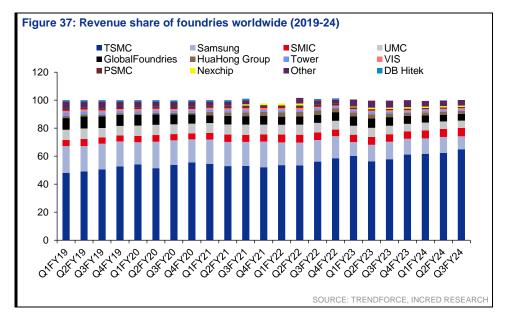

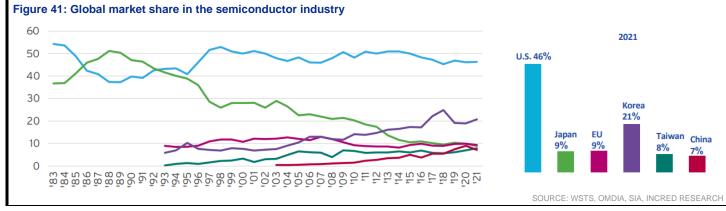

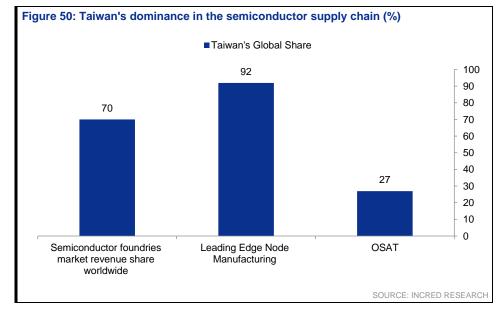

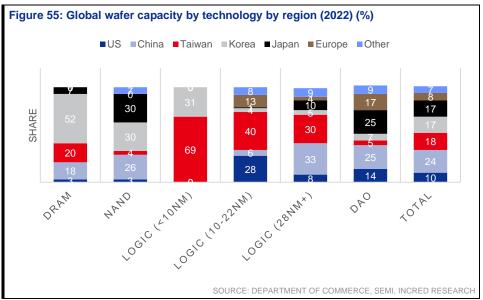

- Tech sovereignty: With growing reliance on imported chips, nations now view semiconductor independence as central to long-term economic and defence resilience. Semiconductor fabrication is especially concentrated in East Asia, with Taiwan and Korea (TSMC and Samsung, respectively) alone contributing to more than 70% of total foundry revenue worldwide.

- Export controls: In response to geopolitical tensions, the US has expanded its use of the Entity List to block high-end chip exports to China elevating chips to the level of strategic assets like nuclear technology.

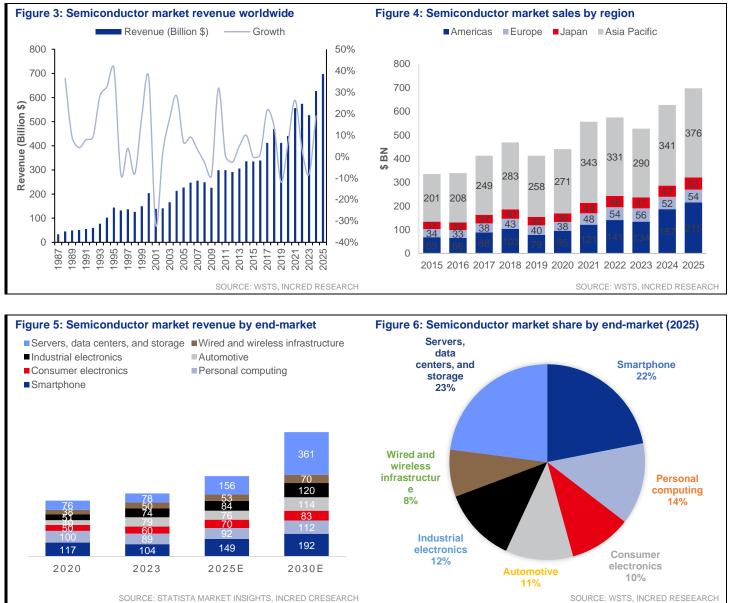

- Economic dependency: In 2023, China imported US\$385bn in semiconductors, making chips its largest import category. In India, net electronics imports touched US\$60bn in FY24, and this widening trade gap was driven by growing dependence on imported chips.

- Supply chain fragility: The chip shortage during 2020-22 exposed how concentrated and fragile the global semiconductor value chain is. Disruptions in East Asia led to multi-quarter delays in electronics and automobile manufacturing worldwide. The incident became a wake-up call for governments to pursue reshoring, friend-shoring, and supply chain resilience.

### Demand drivers >

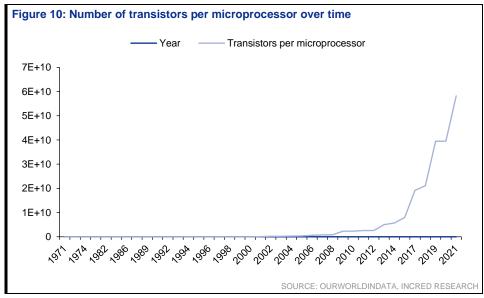

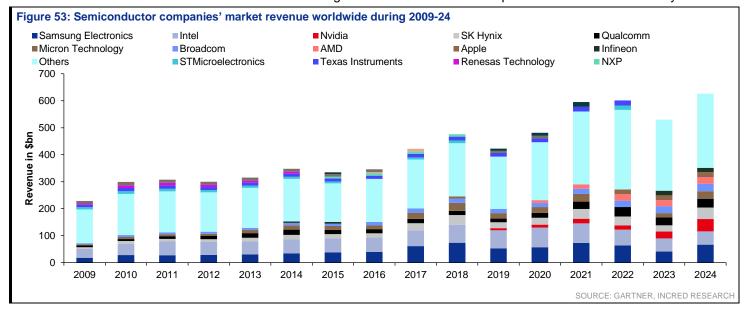

The global semiconductor industry has been highly cyclical due to a variety of factors like high sensitivity to economics cycles, long lead times in supply expansion (building a new fab can take years) and technology transitions. But for the future, the global semiconductor industry continues to experience strong momentum with revenue projected to top US\$700 bn by 2025F. Demand is being propelled by structural tailwinds including digital transformation, growing Al adoption, and increasing localization of supply chains. India, meanwhile, is seeing rapid growth in semiconductor-linked sectors such as consumer electronics and electric vehicles.

Segment-wise, consumer electronics remains the dominant demand contributor worldwide, but it is expected to grow at a CAGR of 3.5% over the next five years as compared to 18.3% growth for servers, data centres and storage segment and a 8.5% growth rate in the automotive industry.

#### SOURCE: STATISTA MARKET INSIGHTS, INCRED CRESEARCH

### Classification of semiconductors by device type >

Semiconductors can be broadly classified into four functional categories:

| Figure 7: Semiconductor classification by device type |                                                    |                                                 |                         |

|-------------------------------------------------------|----------------------------------------------------|-------------------------------------------------|-------------------------|

| Category                                              | Description                                        | Key Applications                                | Global Share<br>(2025F) |

| Integrated Circuits (ICs)                             | Logic, Memory, Analog, and MCU                     | Computing, Phones,<br>Automotives, Data Centres | 85%                     |

| Optoelectronics                                       | Image Sensors, LEDs,<br>Display Drivers, Photonics | Displays, Cameras, Lidar,<br>Optical Fibre      | 7%                      |

| Discrete Semiconductors                               | Single-function<br>Transistors/Diodes              | Power Management,<br>Inverters, EVs             | 5%                      |

| Sensors & Actuators                                   | MEMS, Temperature,<br>Pressure, Gyro               | loT, Robotics, Smart Health,<br>Automotive      | 3%                      |

|                                                       |                                                    | SOURCE: INC                                     | RED RESEARCH            |

### Classification by node size ➤

Originally, the node size used to describe the physical length of the transistor gate or the half-pitch of certain features (like metal interconnectors). However, in modern usage, node size has become more of a marketing term rather than a precise physical measurement, with the actual features varying across different foundries and generations. Chipmakers use it to signal performance and energy efficiency improvements – in line with Moore's Law. Although actual physical scaling has slowed, node labels remain critical to the branding of new chip generations and to benchmark technological advancements.

| Node Size | Year Introduced | Technology Example            | Use-Case Examples                        |

|-----------|-----------------|-------------------------------|------------------------------------------|

| 90nm      | 2003            | Intel Pentium D, TI OMAP      | Entry smartphones, feature phones        |

| 65nm      | 2005            | AMD Athlon 64, TI DSP         | Set-top boxes, mid-tier electronics      |

| 45nm      | 2007            | Intel Core 2, Atom            | Laptops, routers                         |

| 32nm      | 2010            | Intel Core i3/i5/i7 (1st Gen) | Desktop processors                       |

| 28nm      | 2011            | Qualcomm Snapdragon S4        | Smartphones, tablets                     |

| 14nm      | 2014            | Intel Broadwell, Apple A8     | Mobile SoCs, laptops                     |

| 7nm       | 2018            | Apple A12 Bionic, AMD Zen 2   | High-end phones, AI, gaming GPUs         |

| 5nm       | 2020            | Apple A14 Bionic, M1          | Flagship smartphones, ML<br>accelerators |

| 3nm       | 2023            | Apple A17 Pro, TSMC N3        | LLM chips, servers                       |

|           |                 |                               | SOURCE: INCRED RESEARCH                  |

### Functional classification >

As semiconductor design has involved, so have the specialized architectures built atop them. While all modern chips are based on transistors, their architecture and function determine how they interact with software, perform computation, and optimize for power, speed or pace.

| Figure 9: S | Figure 9: Semiconductor classification by function |                           |                                         |  |

|-------------|----------------------------------------------------|---------------------------|-----------------------------------------|--|

| Chip Type   | Description                                        | Example Use Cases         | Examples                                |  |

| CPU         | General purpose compute                            | PCs, phone, servers       | Intel Core, AMD Ryzen                   |  |

| GPU         | Parallel processing for large<br>data blocks       | Gaming, AI/ML, rendering  | NVIDIA RTX, AMD Radeon                  |  |

| NPU         | Optimised for AI inference                         | Smartphone, edge Al       | Apple Neural Engine, Google<br>Edge TPU |  |

| ASIC        | Custom logic for one function                      | Bitcoin mining, 5G modems | Bitmain                                 |  |

| FPGA        | Reprogrammable logic                               | prototyping, telecom      | Intel Stratix                           |  |

|             |                                                    |                           | SOURCE: INCRED RESEARCH                 |  |

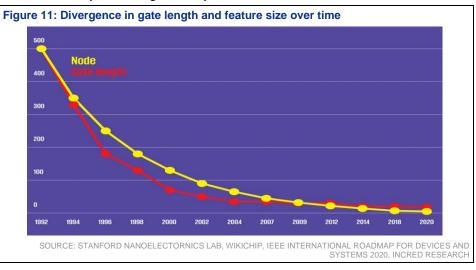

### Moore's Law and technology evolution

Formulated by Intel's co-founder Fordon Moore in 1985, it stated that the number of transistors on a chip would double every 18-24 months, improving performance and reducing costs. This held true for decades, propelling the digital revolution.

This progress was initially measured by using the feature size of the chip, primarily the metal half-pitch and the gate length. For the planar 2-D architecture of the chips used earlier, doubling of number of chips in a unit area meant reducing the

size of these two features by 30% in each successive generation. This classification worked well because the gate length and metal half pitch were roughly equivalent.

Seeking to continue historic gains in speed and device efficiency, chipmakers shrank the gate length more aggressively than other features of the device. For example, transistors made using the so-called 130-nm node actually had 70-nm gates. The result was the continuation of the Moore's Law density-doubling pathway, but with a disproportionately shrinking gate length. This divergence widened with the advent of non-planar (3D) architecture like the FinFET where transistor density is no longer strictly a function of 2D area.

As a result of these advancements, **modern "node names" such as 7nm, 5nm or 2nm no longer correspond to any actual physical dimension on the chip**. Instead, they serve as marketing labels, loosely representing generational improvements in performance, power efficiency and density.

To address the limitations of traditional node naming, the industry has explored alternative metrics like GMT metric which quantifies the process improvement based on three factors – Gate Pitch, Metal Pitch and Number of Tiers. For example, the IRDS road map shows that the 5-nm chips have a contacted gate pitch of 48 nm, a metal pitch of 36nm, and a single tier—making the metric G48M36T1.

| •       | ture size vs node size |             |      |  |

|---------|------------------------|-------------|------|--|

| Process | Gate pitch             | Metal pitch | Year |  |

| 7 nm    | 60 nm                  | 40 nm       | 2018 |  |

| 5 nm    | 51 nm                  | 30 nm       | 2020 |  |

| 3 nm    | 48 nm                  | 24 nm       | 2022 |  |

| 2 nm    | 45 nm                  | 20 nm       | 2025 |  |

| 1 nm    | 42 nm                  | 16 nm       | 2027 |  |

**Looking ahead: The future of semiconductor scaling -** As the industry approaches the physical limits of traditional CMOS scaling, alternative strategies are being pursued to sustain progress:

- **3D integration**: Stacking multiple layers of transistors vertically to increase density without shrinking individual transistors. This approach can lead to significant improvements in performance and energy efficiency.

- Advanced Packaging: Techniques like chiplet integration and heterogeneous integration allow combining different types of chips in a single package, optimizing performance and functionality.

- **New materials**: Exploration of materials beyond silicon, such as cubic boron arsenide (c-BAs), which offers high carrier mobility and thermal conductivity, potentially outperforming silicon in certain applications.

- **Beyond CMOS Technologies**: Development of novel computing paradigms, including quantum computing and neuromorphic computing, which could revolutionize processing capabilities.

# Semiconductor value chain – Structure, business models & global dynamics

### Overview of the semiconductor manufacturing process >

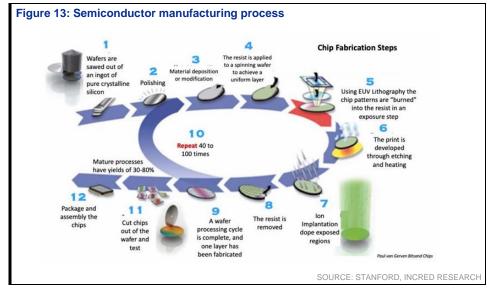

Semiconductor manufacturing is a highly complex and precise process that transforms raw materials into integrated circuits.

### 1. Raw material preparation :

- Unlike solar-grade silicon (6N purity), which is produced by refining quartz derived from common sand, semiconductor-grade silicon (9N purity) is made from specially mined high-purity quartz — primarily sourced from Spruce Pine, North Carolina, the world's leading region for such material. Ingots are made using this silicon.

- These ingots are sliced into ultra-thin silicon wafers, serving as the base for chip manufacturing.

### 2. Wafer fabrication (front-end processing):

- Photolithography: A light-sensitive material (photoresist) is applied to the wafer, and patterns are etched using ultraviolet light.

- Etching: Chemical or plasma etching removes specific parts of the wafer to define circuit patterns.

- Deposition: Thin layers of materials (insulators, metals, semiconductors) are deposited to build up circuit structures.

- Ion implantation: lons are implanted into the wafer to modify electrical properties of regions.

- o Multiple layers are stacked precisely to form complex integrated circuits.

### 3. Wafer testing:

• Electrical testing is performed on each die while still part of the wafer to identify functional units.

### 4. Assembly and packaging (back-end processing):

- Dicing: The wafer is cut into individual dies.

- Die bonding: Each die is mounted onto a substrate or lead frame.

- Wire bonding or flip-chip: Electrical connections are made between the die and the package.

- Encapsulation: The package is sealed to protect the chip.

### 5. Final testing and quality control:

Packaged chips undergo rigorous functional and environmental testing to ensure reliability and performance before shipment.

# **InCred** Equities

Technology | India Technology - Others | May 12, 2025

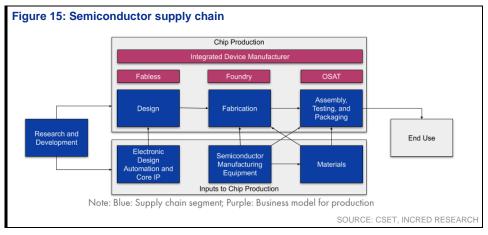

### Overview of the semiconductor value chain >

The semiconductor industry is built on a globally distributed, highly specialized value chain. The semiconductor industry requires deep specialization at each stage due to the complexity, capital intensity, and skill requirements involved. The process begins with chip architecture and design, moves into fabrication, and ends with packaging, testing and system-level integration. Each stage is a highly specialized field with geographical concentrations and corporate specializations across different parts of the supply chain. As a result, companies are moving away from vertical integration – illustrated by major players like AMD, which spun off its manufacturing arm (now GlobalFoundries) to focus solely on chip design.

# **InCred** Equities

#### Technology | India Technology - Others | May 12, 2025

| Eiguro 44            | S. Somioonductor cumply of                                                  | hain avanviou                                                                   |                                                                                                  |

|----------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| •                    | 5: Semiconductor supply o                                                   |                                                                                 | Indiala Statua                                                                                   |

| Stage                | Description                                                                 | Key Global Players                                                              | India's Status                                                                                   |

| Raw<br>Materials     | Semiconductor grade<br>polysilicon, photoresists, rare<br>gases, substrates | Hemlock Semiconductor,<br>Tokuyama Corporation, Shin-<br>Etsu, JSR, Air Liquide | Very low presence; India<br>currently lacks PPB-level purity<br>required for chip fabrication    |

| Equipment<br>(Tools) | Lithography, deposition, etching, testing machines                          | ASML (Dutch), Applied<br>Materials (US), Tokyo Electron<br>(Japan)              | Very low presence; full import<br>dependency, especially for<br>lithography                      |

| EDA/IP               | Electronic design automation tools and IP cores                             | Synopsys, Cadence, Arm                                                          | Moderate presence via<br>workforce; no Indian company in<br>the top-tier segment                 |

| Chip<br>Design       | Architecture, logic and RTL design of semiconductors                        | NVIDIA, AMD, Qualcomm                                                           | Strong global hub; 20% of global<br>workforce; 50+ global design<br>centre in India              |

| Foundry<br>(Fab)     | Wafer fabrication using<br>lithography and etching on<br>wafers             | TSMC, Samsung, Intel                                                            | In-development: First fab unit by<br>Tata-PSMC is expected to start<br>operations by 2026F       |

| ATMP                 | Assembly, test, marking and packaging                                       | ASE, Amkor, JCET                                                                | Four ATMP facilities approved<br>under ISM with US\$7bn+ of<br>investments                       |

| System<br>Assembly   | Final integration: PCBs, casings, and devices                               | Foxconn, Pegatron, Dixon                                                        | Mature segment: Second-<br>largest smartphone producer<br>globally; string PLI-backed<br>exports |

|                      |                                                                             |                                                                                 | SOURCE: INCRED RESEARCH                                                                          |

### Figure 17: R&D, capex and value addition of different segments (% of industry total, 2019)

| Segment                       | R&D                         | Capex           | Value Addition  |

|-------------------------------|-----------------------------|-----------------|-----------------|

| Design                        | 53                          | 13              | 50              |

| Front-end (wafer fabrication) | 13                          | 64              | 24              |

| Back-end (ATMP)               | 3                           | 13              | 6               |

| EDA & core IP                 | 3                           | 1               | 4               |

| Equipment tools               | 9                           | 3               | 11              |

| Materials                     | 1                           | 6               | 5               |

| Pre-competitive research      | 18                          | 0               | 0               |

|                               | SOURCE: SEMICONDUCTOR INDUS | TRY ASSOCIATION | INCRED RESEARCH |

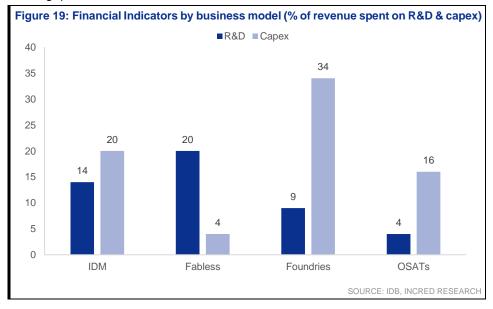

### Manufacturing business models (IDM, fabless, foundry) ➤

Four major business models have evolved in the manufacturing segment of the semiconductor industry:

• Integrated device manufacturers (IDM):

A vertically integrated model where the company designs, fabricates, tests, and packages its own chips. This approach offers tighter control over IP, quality, supply chain security and product performance. It is highly advantageous for mission critical or proprietary applications where tight coordination is required. However, the model is highly capital and R&D-intensive, requiring billions of dollars in upfront investment and long payback periods. Only a few players globally operate at scale in this model – which include Intel, Samsung, and Texas Instruments.

• Fabless model:

This model focuses entirely on chip design, while outsourcing fabrication and back-end processes to third-party foundries and OSATs. This model lowers capital expenditure and allows companies to specialize in IP development, architecture optimization and software-hardware co-design. It has become the dominant structure for innovation-driven companies, particularly in AI, mobile and graphics computing. Key examples include NVIDIA, Qualcomm, and AMD.

• Pure play foundry model:

These companies focus exclusively on fabrication services and manufacture chips designed by their clients. Foundries operate high-volume fabs and require enormous capex, technical leadership, and consistent demand to maintain profitability. Leading foundries like TSMC, GlobalFoundries, and SMIC have become the backbone of semiconductor production.

• Outsourced semiconductor assembly and testing (OSAT):

The OSAT model handles the post-fabrication phase of chip production or the back-end manufacturing. This includes assembly, packaging, and testing. It is a low-margin, high-volume business, often serving fabless and IDM clients alike. Global leaders include ASE Group, Amkor, and JCET. India is actively building capacity here through projects like Micron's ATMP facility and Tata's TSAT plant in Assam.

From a geographic perspective, each model has gravitated towards specialized global hubs: IDMs remain centered in the US, Korea; fabless companies dominate in the US and China; foundry capacity is concentrated in Taiwan and South Korea; OSAT hubs are primarily in Taiwan, Malaysia, Singapore, and South Korea.

### Global supply chain concentration ➤

The semiconductor supply chain is highly concentrated, with key choke points dominated by a few global players.

| Figure 20: Global semiconductor supply chain choke points |                                   |                        |                           |

|-----------------------------------------------------------|-----------------------------------|------------------------|---------------------------|

| Segment                                                   | Global Leader                     | Estimated Market Share | Risk Implication          |

| Lithography                                               | ASML (Netherlands)                | 100% (EUV)             | Single-point failure risk |

| Foundry                                                   | TSMC (Taiwan)                     | 64% (<10nm tech)       | Taiwan dependency risk    |

| EDA/IP                                                    | Synopsys, Cadence,<br>Siemens EDA | 85%                    | US dominance              |

| Materials                                                 | JSR, Shin-Etsu                    | >70% in some           | Japan-centric             |

|                                                           |                                   |                        | SOURCE: INCRED RESEARCH   |

These concentrations make the industry vulnerable to geopolitical shocks, natural disasters, or export restrictions, as highlighted by the ongoing US advanced chips export restrictions to China and COVID-related disruptions.

### India's semiconductor and AI landscape

### Overview of India's semiconductor & Al value chain >

India's ambition to become a global hub for semiconductor and AI technologies is underpinned by rising electronics consumption, strategic import dependency and significant policy interventions. However, the current landscape reflects a foundational phase with strengths in design and assembly but notable weaknesses in the high value addition upstream manufacturing and infrastructure.

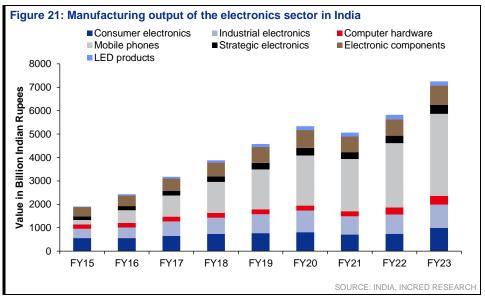

India's domestic electronics market has expanded at a CAGR of ~13% over FY17 to FY23. However, this expansion was driven largely by assembly-centric activities, rather than upstream component manufacturing.

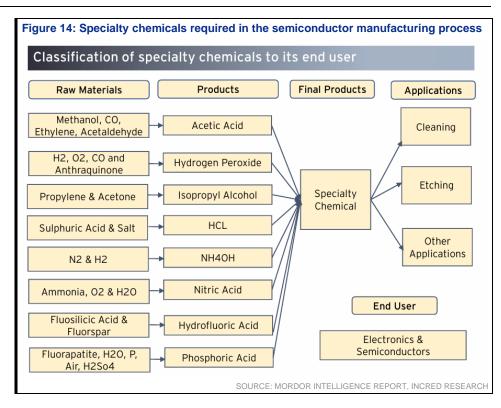

India's current presence across the semiconductor value chain is highly uneven. The country enjoys a strong position in chip design and embedded software, contributing to ~20% of the global design workforce. Cities like Bengaluru, Hyderabad, Chennai and Noida host R&D centres of major multinational companies like AMD, NVIDIA, and Qualcomm. However, while India excels in design talent, the value captured in this segment is comparatively low as core IP ownership remains with foreign companies. But Indian startups like Mindgrove and Saankhya Labs are making inroads in chiplet and IoT design to overcome this issue. In fabrication, India currently lacks an operational frontend logic fab, but the upcoming TATA-PSMC fab unit in Dholera will help overcome the absence in this segment. On the ATMP/OSAT or the back-end manufacturing front, India has made most important strides. With Sahasra Semiconductors and Suchi Semicon already starting operations and four major projects to be operational by FY27F, including Micron, CG-Renesas, Tata's ATMP facility, and Kaynes Technology, India is poised to become a fast-growing hub for back-end manufacturing. In terms of final assembly and integration, India already has strong capabilities in electronics manufacturing services (EMS). Major players such as Foxconn, Pegatron, and Dixon Technologies have increased their footprint in the country, especially after the production-linked incentive or PLI schemes launched by the government. However, a major gap remains in raw materials and semiconductor-grade equipment. India imports nearly all its high-purity gases, wafers, and chemicals required for chip fabrication. While domestic chemical manufacturing exists, it produces chemicals with parts per million purity as compared to parts per billion purity required for semiconductor manufacturing.

India's current AI ecosystem is advancing rapidly in software and research. However, the country lacks national-scale compute infrastructure, foundational models, and large-scale Indian language datasets.

### India's electronics manufacturing push >

India sees electronics as the backbone of its digital future – key to economic strength and national security. Over the past decade, the country has pushed hard to grow its electronics manufacturing, aiming to reduce imports, add more local value, and compete globally. The National Policy on Electronics (NPE) was the government's strategic pivot. Initially launched in 2012, the policy failed to generate sufficient traction – partly due to a lack of capital subsidies, scale incentives and coordination with states. Learning from these shortcomings, the government launched a revised version – NPE 2019, aiming to achieve US\$400bn in electronics production by 2025F.

To operationalize this vision, the government introduced downstream initiatives:

- PLI for large-scale electronics manufacturing (2020) Aims to bolster domestic electronics production by offering 4-6% incentive on incremental sales of mobile phones and specified electronic components over a five-year period.

- Scheme for promotion of manufacturing of electronic components and semiconductors (SPECS) – This scheme offered a 25% capital subsidy for specific segments.

Modified electronics manufacturing clusters (EMC 2.0) scheme – It provided financial assistance for establishing both electronics manufacturing clusters (EMCs) and common facility centres (CFCs) across the country.

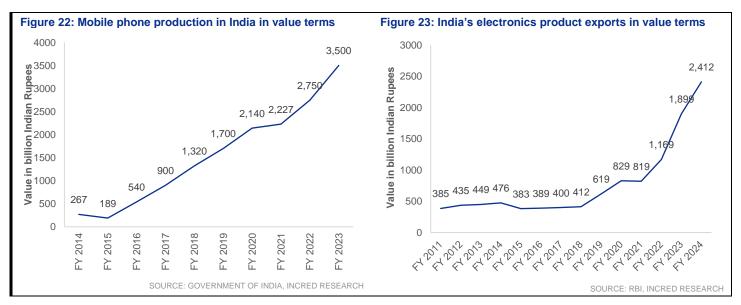

The results have been significant, with data underscoring India's growing electronics manufacturing base:

- Electronics manufacturing grew at a CAGR of 14.8% over FY17 and FY23.

- Mobile phone manufacturing emerged as the strongest segment, contributing Rs3.5tr in FY23, growing at a CAGR of 44% over FY15 and FY23.

- Electronics exports reached US\$29bn in FY23, up 27% YoY, with the share of electronics in total exports rising from 4.9% in FY22 to 6.7% in FY24.

However, the value addition challenge remains. India's Electronics System Design and Manufacturing sector is still largely assembly-led, with domestic value addition estimated at just 15-16%. Critical upstream inputs such as semiconductors, displays, and camera modules are mostly imported currently, with limited domestic capability in tooling, materials or fabrication.

India's policy landscape, however, shows a trend of learning and iteration. The government has repeatedly revised and recalibrated its approach. The initial NPE 2012 was followed by the more structured NPE 2019. The first semiconductor fab policy launched in 2021, which saw no global interest, was revised in 2023 with

improved fiscal terms and a pivot to mature nodes (28nm+). Similarly, PLI schemes have been expanded and restructured to improve adoption.

### India's semiconductor mission >

India launched the India Semiconductor Mission (ISM) in 2021 with an outlay of Rs760bn and aims to build a semiconductor and display ecosystem in the country. This holistic approach of the mission aims to cover the entire value chain – from design to manufacturing and packaging.

It comprises four main schemes -

• Semiconductor fab scheme -

Objective: To attract large investments for setting up semiconductor wafer fabrication facilities in the country to strengthen the electronics manufacturing ecosystem and help establish a trusted value chain.

Key incentives & eligibility:

| Figure 24: ISM                                   | - Semiconductor fab scheme subsidies                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                  | 2021                                                                                                                                                                                                                                                                                                                                                                                                             | 2023                                                                                                                                                                                                                                                                                         |

| Node Size                                        | 65/45/28 nm or advanced (including intermediate nodes)                                                                                                                                                                                                                                                                                                                                                           | For all node size                                                                                                                                                                                                                                                                            |

| Operational<br>Experience                        | Applicant companies/consortia /joint ventures<br>should have the following experience:<br>A. Own and operate 65/45/28nm (including<br>intermediate nodes) or advanced nodes<br>process(es) in silicon CMOS semiconductor fab o<br>B. Own or possess production grade licensed<br>technologies for 28nm process and demonstrate<br>the roadmap to advanced nodes technologies<br>through licensing or development | Applicant companies/consortia/joint<br>ventures should have the following<br>experience:<br>Own or possess production grade<br>licensed technologies for proposed<br>technology process and demonstrate<br>the roadmap to advanced nodes<br>technologies through licensing or<br>development |

| Fiscal support<br>from<br>Government of<br>India | Fiscal support:<br>28nm or lower - up to 50%;<br>Above 28 nm to 45nm - up to 40%;<br>Above 45 nm to 65nm - up to 30%                                                                                                                                                                                                                                                                                             | Fiscal support as percentage of project cost - 50 %                                                                                                                                                                                                                                          |

|                                                  | SOURCE: GO                                                                                                                                                                                                                                                                                                                                                                                                       | VERNMENT OF INDIA, INCRED RESEARCH                                                                                                                                                                                                                                                           |

Relaunch history: When the scheme was initially launched in 2021, the focus was on attracting advanced node semiconductor fabs. Key features included graded fiscal support depending on the chip size, emphasis on cutting edge technologies and large-scale investment (minimum capital investment of Rs200bn) and strict eligibility – companies needed prior fab experience and partnerships with leading tech firms.

However, this approach received a limited response due to the capital-intensive nature of advanced fabs, and lack of supporting infrastructure and supply chain maturity at the time.

In response to the industry feedback and global semiconductor supply challenges, the government relaunched the scheme, easing the requirements in terms of node size and operational experience and removing the graded fiscal support, making it more investor friendly. This strategic realignment reflects India's urgency to kickstart the ecosystem and focusing on mature technologies where domestic demand is high.

Approved projects:

- 1) Tata Electronics in partnership with PSMC

- Display fab scheme -

Objective: To attract large investments in setting up display fabrication facilities in the country to strengthen the electronics manufacturing ecosystem.

Key incentives and eligibility:

| Figure 25: ISM – Display f                                                  | ab scheme subsidies                                                                                                                                                                                        |                                                       |  |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|

|                                                                             | 2021                                                                                                                                                                                                       | 2022                                                  |  |

| Technology                                                                  | Generation 8 or above for TFT LCD OR Generation 6 or above for AMOLED                                                                                                                                      |                                                       |  |

| Capacity                                                                    | 60,000 panels/month or more for TFT LCD 30,000 panels/month or more for AMOLED                                                                                                                             |                                                       |  |

| Applicant companies/consortia/joint ventures should have the<br>experience: |                                                                                                                                                                                                            |                                                       |  |

| Operational experience                                                      | A. Own and operate a commercial display fab facility with TFT LCD technology of Generation 6 or above or                                                                                                   |                                                       |  |

|                                                                             | B. Own or possess licensed technologies for Generation 8 of TFT LCD technology or Generation 6 of AMOLED technology; and demonstrate the roadmap to advanced technologies through licensing or development |                                                       |  |

| Capital investment threshold                                                | Minimum capital investment of Rs100bn                                                                                                                                                                      |                                                       |  |

| Fiscal support from Gol                                                     | Fiscal support as percentage of project cost -<br>up to 50% with a maximum support of Rs120<br>bn                                                                                                          | Fiscal support as a percentage of project cost is 50% |  |

|                                                                             | SOURCE: GOVERNMEN                                                                                                                                                                                          | IT OF INDIA, INCRED RESEARCH                          |  |

Relaunch history: The scheme was initially launched in 2021 but was relaunched in 2022 with the only change being removal of the incentive cap of Rs120bn.

Status: No deals have currently been approved under this scheme.

Additional observations: Displays constitute a significant portion of the total Bill of Materials (BoM) of electronic products. For instance, displays account for over 25% of the BoM in case of smartphones and over 50% in case of LCD / LED TVs. As per estimates, India's display panel market is estimated to be ~US\$7bn (Rs525bn) and is expected to grow to ~US\$15bn (Rs1.13tr) by 2025F. Current requirements are met exclusively through imports. This highlights the importance of the government to help set up a display fab plant in India.

• Compound semiconductor & ATMP scheme -

Objective: To attract investments for setting up compound semiconductors / silicon photonics (SiPh) / sensors (including MEMS) fabs and semiconductor ATMP/OSAT facilities in the country to strengthen the electronics manufacturing ecosystem and help establish a trusted electronics value chain in the areas of application of these fabrication and packaging technologies.

Key incentives and eligibility:

Compound semiconductors/silicon photonics (SiPh)/sensors (including MEMS) fab –

| Figure 26: ISM – Compou      | und semiconductor/ SiPh/ sensors scheme subsidies                                                                                                                                                                                                                                                                                             |                                           |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|

|                              | 2021                                                                                                                                                                                                                                                                                                                                          | 2022                                      |  |

| Technology                   | Wafer size: 150/200mm or more; Capacity: 500 or more wafer starts/month<br>(in 100 mm equivalent)                                                                                                                                                                                                                                             |                                           |  |

| Operational experience       | The applicant companies/joint ventures should have the following<br>experience:<br>A. Own and operate commercial compound semiconductors/silicon<br>photonics (SiPh)<br>/ Sensors (including MEMS) fab/discrete semiconductors fab or silicon<br>semiconductor fab or<br>B. Own or possess licensed process technologies for the proposed fab |                                           |  |

| Capital investment threshold | Minimum capital investment of Rs1bn for compound semiconductors / silicon<br>photonics (SiPh) / sensors (including MEMS)/ discrete semiconductors fab                                                                                                                                                                                         |                                           |  |

| Fiscal support from Gol      | 30% of capital expenditure                                                                                                                                                                                                                                                                                                                    | 50% of capital ependiture                 |  |

|                              | SOUR                                                                                                                                                                                                                                                                                                                                          | CES: GOVERNEMNT OF INDIA, INCRED RESEARCH |  |

Semiconductor assembly, testing, marking and packaging (ATMP) / Outsourced semiconductor assembly and test (OSAT) facility –

| Figure 27: ISM – OSAT/ATMP scheme subsidies |                                                                                                                                                                                                                                                                                                                                            |                                              |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|                                             | 2021                                                                                                                                                                                                                                                                                                                                       | 2022                                         |

| Operational experience                      | Applicant companies/joint ventures should have the following experience:<br>A. Own and operate a commercial semiconductor packaging unit or<br>B. Own or possess licensed technologies for the proposed semiconductor<br>packaging unit and demonstrate the roadmap to advanced packaging<br>technologies through licensing or development |                                              |

| Capital investment threshold                | Minimum capital investment of Rs500m                                                                                                                                                                                                                                                                                                       |                                              |

| Fiscal Support from Gol                     | 30% of capital 50% of capital expenditure                                                                                                                                                                                                                                                                                                  |                                              |

|                                             |                                                                                                                                                                                                                                                                                                                                            | SOURCE: GOVERNMENT OF INDIA, INCRED RESEARCH |

Relaunch history: Initially launched in 2021 and modified in 2022, the only modification was the increase in fiscal support from 30% of the capex to 50% of the capex,

Approved deals:

- Tata Semiconductor Assembly and Test (TSAT)

- CG Power & Renesas Electronics (Japan)

- Kaynes Semicon

- Micron Technology

Additional observations: This has been the most successful scheme in the ISM with four approved projects worth more than Rs600bn.

Design-linked initiative scheme –

Objectives: The design-linked incentive (DLI) scheme shall offer financial incentives as well as design infrastructure support across various stages of development and deployment of semiconductor design for Integrated Circuits (ICs), Chipsets, System on Chips (SoCs), Systems & IP Cores and semiconductor-linked design over a period of five years with the objectives such as:

- Nurturing 100 domestic companies of semiconductor design for Integrated Circuits (ICs), Chipsets, System on Chips (SoCs), Systems & IP Cores and semiconductor-linked design, and facilitating the growth of not less than 20 such companies to achieve a turnover of more than Rs15bn in the next five years.

- Achieving significant indigenization in semiconductor and electronic products and IPs deployed in the country, thereby facilitating import substitution and value addition in the electronics sector in the next five years.

- Strengthening the design infrastructure through incubators for semiconductor design and facilitating access to startups and MSMEs.

Key initiatives and incentives:

| Figure 28: ISM – DLI scheme suppor<br>Categories of support | rt                                                        |

|-------------------------------------------------------------|-----------------------------------------------------------|

| Scheme component                                            | Description                                               |

|                                                             | (i) National EDA Grid                                     |

| Design infrastructure support for startups /                | (ii) IP Core Repository                                   |

| MSMEs                                                       | (iii) Prototyping                                         |

|                                                             | (iv) Post-Silicon Validation                              |

| Product design-linked incentive                             | Reimbursement of 50% of the eligible expenditure subject  |

|                                                             | to a ceiling of Rs150m incentive per application.         |

| Deployment-linked incentive                                 | Reimbursement of 6% to 4% of net sales over five years,   |

| Deployment-linked incentive                                 | subject to a ceiling of Rs0.3bn incentive per application |

|                                                             | SOURCE: GOVERNMENT OF INDIA, INCRED RESEARCH              |

Relaunch history: This scheme is still in its first version and hasn't been modified till now.

Approved projects: A total of 69 companies have been approved for EDA Tool Support. This provides access to software tools and services for designing electronic systems specifically focusing on ICs and semiconductor chips. Apart from this, 17 companies have been provided with financial support under this scheme.

Additional observations: India already accounts for ~20% of the global semiconductor design workforce, and this scheme helps strengthen the IP monetization ecosystem. Moreover, the total electronic design market in India, estimated at Rs350bn in 2020 and growing at a CAGR of ~15.4%, necessitates fostering the domestic semiconductor design industry to not only meet the domestic requirement and service global customers but also achieve self-reliance and mitigate the security concerns of this strategic sector.

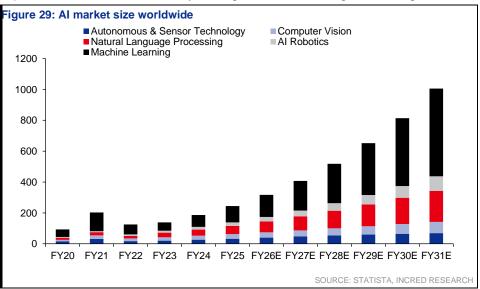

### India Al mission >

Objective: The IndiaAI mission aims to build a comprehensive ecosystem that fosters AI innovation by democratizing computing access, enhancing data quality, developing indigenous AI capabilities, attracting top AI talent, enabling industry collaboration, providing startup risk capital, ensuring socially impactful AI projects, and promoting ethical AI.

Launched with a budget of Rs103bn, key components of the IndiaAI mission include:

- IndiaAl compute capacity Focuses on building a scalable Al ecosystem with 10,000+ graphics processing units or GPUs via public-private partnerships, offering Al services and resources.

- IndiaAl innovation centre Focuses on developing and deploying indigenous large multimodal models (LMM) and domain-specific foundational models.

- IndiaAI datasets platform Focuses on streamlining the access to highquality non-personal datasets for AI innovation.

- IndiaAI application development initiative Develops, scales, and promotes impactful AI solutions for large-scale socio-economic transformation.

- IndiaAI future skills This pillar aims to expand AI education at all academic levels and establish data and AI labs in Tier-2 and Tier-3 cities.

- IndiaAI startup financing This pillar accelerates deep-tech AI startups by streamlining access to funding for innovative AI projects.

- Safe & trusted AI Focuses on ensuring responsible AI via projects, tools, checklists, and governance frameworks for responsible development and use.

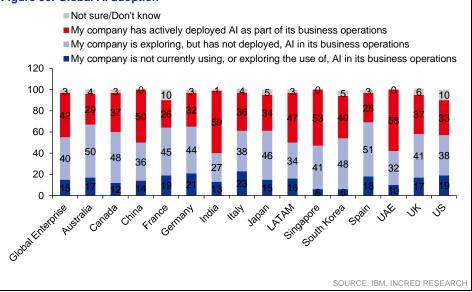

Additional observations : **The global AI market capitalization is expected to grow at a CAGR of 27% over FY24 to FY31F.** Alongside this expansion, the global adoption of AI has accelerated, with 42% of global enterprises already integrating AI into their operations. India, in specific, leads in this area with 59% of its companies already integrating AI into their operations and another 27% exploring to do the same, which is much higher than its global peers such as the US (33%) and China (26%).

In terms of workforce, India is playing a fast-expanding role in this ecosystem. According to the Stanford's HAI report, India leads the world in AI skill penetration, with relative AI skill penetration at 2.5 times the global average, lagging just behind US. Moreover, India recorded the highest growth in AI hiring globally in 2024 at 33.4% YoY.

Despite these advances, a significant talent gap remains. While India's AI job market is expected to create 2.3m jobs by 2027F, the available skilled workforce is projected to reach only 1.2m, indicating a gap which the government aims to bridge through reskilling and upskilling via this mission.

As a part of its IndiaAI compute capacity initiative, the government recently concluded the bidding for provisioning 10,000+ GPUs via public-private partnerships. Yotta Data Services, E2E Networks, and NxtGen Cloud Technologies were selected to deliver AI compute resources at subsidized rates (under US\$1/hour) — among the lowest globally — to support startups, research, and public sector innovation. This move is expected to accelerate AI experimentation and accessibility amid global GPU shortage and rising demand.

Technology | India Technology - Others | May 12, 2025

### Figure 30: Global Al adoption

### Role of state governments >

While the central government's schemes and policies have provided the strategic blueprint and the fiscal backbone for semiconductor development, the role of individual states has been equally critical in shaping on-ground execution. As seen in electronics manufacturing, many clusters have developed in the country like Tamil Nadu, Maharashtra, and Uttar Pradesh which attracted investments by complementing the central government's emphasis on electronics manufacturing through schemes like EMC 2.0, SPECS, and PLI schemes.

Semiconductor manufacturing is deeply dependent on infrastructure, clean water, uninterrupted power and land availability – factors managed primarily at the state level. In recent years, several Indian states have launched dedicated semiconductor and electronics policies, offering capital incentive, non-fiscal support like logistical support and infrastructure support to attract investments in their states.

Gujarat –

Gujarat already had an electronics policy which it launched in 2020 and became the first state in India to launch a dedicated semiconductor policy in 2022. The semiconductor policy provides capital assistance at the rate of 40% of capex assistance given by the Government of India or Gol, subsidy on land purchase, water, power, and additional non-fiscal incentives.

| -          | e incentives for semiconductor manufacturing Amount                                   |  |

|------------|---------------------------------------------------------------------------------------|--|

| Туре       |                                                                                       |  |

| Investment | 40% of capex assistance by the Government of India (20% of the total project cost)    |  |

| Power      | Power tariff subsidy of Rs2/unit for 10 years; electricity duty exemption             |  |

| Land       | 75% on first 200 acres, 50% on additional                                             |  |

| Water      | Rs12/cubic metre for the first five years; 50% subsidy on capex of desalination plant |  |

| Fees       | One-time reimbursement of 100% of stamp duty and registration fee                     |  |

| ĺ          | SOURCE: GOVERNMENT OF GUJARAT, INCRED RESEARCH                                        |  |

Apart from the policy support, Gujarat also has a strong manufacturing and business environment. It was ranked top in Ease of Doing Business, Logistics Performance Index, Good Governance Index and in terms of infrastructure, Gujarat has a 1,600km+ coastline with 48 seaports, 5,300km+ railway lines, and 19 airports.

In terms of the semiconductor value chain, Gujarat is the chemical hub of India producing nearly 50% of chemicals in the country. It has a well-established supply chain for several key chemicals consumed by the semiconductor industry such as sulphuric acid, hydrochloric acid, aromatic compounds, aliphatic compounds, etc. Many domestic companies have expressed interest in augmenting their facilities to meet the demand from the semiconductor sector. It has one upcoming semiconductor fab and several ATMP plants to solidify its position in the entire value chain.

With advantages such as these and the early-mover advantage, Gujarat has managed to attract four of the five investments approved by the Government of India under the ISM which are currently under construction. The state also has received investments from other companies like **Sahasra Semiconductors (ATMP) and Suchi Semicon (ATMP)** which have already started operations and several other MoUs were signed recently in the Gujarat Semicon Connect Conference 2025, including Jabil India's Rs10bn initiative to set up a new silicon photonics unit, NextGen's Rs100bn intent to set up a compound semiconductor fab and optoelectronics facility, and Taiwan Surface Mounting Technology's Rs5bn plan to set up a new EMS unit in Gujarat.

Assam –

Assam has emerged unexpectedly as a semiconductor destination by leveraging its location and India's Act East Policy. The northeastern region has the advantage of grabbing the opportunity of the growing ASEAN market.

| Туре       | Amount                                                                                               |  |

|------------|------------------------------------------------------------------------------------------------------|--|

| Investment | 40% of capex assistance by the Government of India (20% of the total project cost)                   |  |

| Power      | Incentives in power tariff up to 50%                                                                 |  |

| Land       | Nominal prices; freehold transfer of land rights on case-to-case basis                               |  |

| Water      | Rs5/cubic metre for the first 5fiveyears; further subsidy on water tariff on a case-to-case<br>basis |  |

| Fees       | 100% exemption of stamp duty                                                                         |  |

| Others     | SGST reimbursement, payroll assistance                                                               |  |

|            | SOURCE: GOVERNMENT OF ASSAM, INCRED RESEARC                                                          |  |

The state of Assam has been successful in attracting Tata Electronics to set up its OSAT facility at Jagiroad with an investment outlay of Rs270bn.

• Tamil Nadu –

The Tamil Nadu Electronics Hardware Manufacturing Policy 2020 and the special incentives for sunrise sectors under the Tamil Nadu Industrial Policy 2021 have played a vital role in attracting sizeable investments from key players in the electronics hardware manufacturing space due to which Tamil Nadu has become one of the most successful Indian states in the ESDM sector, with the state's industrial corridors attracting investments from major global players such as Foxconn and Pegatron. In FY23-24, Tamil Nadu exported US\$9.56bn of electronic items, which accounted for nearly 33% of the total national share of electronics exports.

Now, with the Tamil Nadu Semiconductor and Advanced Electronics Policy in 2024, the state aims to foray into advanced electronics manufacturing encompassing design, component and equipment manufacturing and the strategic nature of the semiconductor industry.

| Figure 33: Tamil Nadu government incentives for semiconductor manufacturing |                                                                                                                                        |  |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| Туре                                                                        | Amount                                                                                                                                 |  |

| Investment                                                                  | 50% of capex assistance by the Government of India (25% of the total project cost)                                                     |  |

| Special training incentive                                                  | Rs10,000 per person for 12 months for residents of Tamil Nadu                                                                          |  |

| Product testing & prototyping<br>Incentive                                  | A subsidy of 25% of the capex for establishing product testing and prototyping<br>facilities, subject to a ceiling of Rs10m.           |  |

| Power                                                                       | Electricity tax exemption for a period of five years                                                                                   |  |

| Others                                                                      | Land cost incentive, stamp duty incentive, enhanced quality certification<br>incentive, enhanced IP incentive, and interest subvention |  |

|                                                                             | SOURCE: GOVERNMENT OF TAMIL NADU, INCRED RESEARCH                                                                                      |  |

• Karnataka -

Karnataka, particularly Bengaluru, has firmly positioned itself as India's primary semiconductor design and fabless innovation hub. The state hosts over 85 fabless chip design houses and more than 400 R&D centres, making it the core of India's semiconductor IP development ecosystem. Major global companies like Intel, Qualcomm, Texas Instruments, Synopsys, MediaTek, and Analog Devices have significant R&D operations in Bengaluru.

The Karnataka Electronics System Design and Manufacturing (ESDM) Policy 2017–22 provided vital support for semiconductor R&D, infrastructure development, and startup incubation. Going ahead, Karnataka is actively promoting next-generation semiconductor segments like AI accelerators,

photonics, and high-performance computing chipsets through enhanced research collaboration and focused skilling initiatives.

Maharashtra –

Maharashtra, with its strong industrial base around Pune and Aurangabad, has shown strong intent to attract semiconductor projects through its Electronics Policy 2016 and more recently through focused efforts toward semiconductorspecific investments. Although the state initially succeeded in attracting significant proposals—such as the joint venture between the Adani Group and Tower Semiconductor—that partnership has since been paused as the Adani Group is reconsidering the strategic implications and the state is now awaiting major new investments. Maharashtra remains a prime contender for ATMP units, semiconductor design centres, and supply chain manufacturing hubs, supported by its skilled workforce, excellent port logistics through JNPT, and robust financial ecosystem anchored by Mumbai. The state is also working on finalizing a dedicated semiconductor incentive policy to further strengthen its competitiveness.

Uttar Pradesh –

Uttar Pradesh, backed by its Electronics Manufacturing Policy 2020 and the newly launched UP Semiconductor Policy 2024, is rapidly scaling its capabilities in electronics and semiconductor manufacturing. The state is already home to Samsung's Noida plant, the world's largest mobile factory, and is developing new industrial corridors near Jewar Airport to attract high-tech investments.

The UP Semiconductor Policy 2024 offers significant incentives such as a 50% capital subsidy (matching central government incentives), land cost reimbursement up to 75%, 100% stamp duty waiver, infrastructure support, and power tariff subsidies to attract fabs, ATMPs, and design units.

Notably, Uttar Pradesh has attracted the proposed HCL-Foxconn Semiconductor Fab, which is currently awaiting central government approval. The project, if cleared, would firmly establish Uttar Pradesh as a major semiconductor manufacturing state alongside its existing electronics strengths.

### Tracking India's semiconductor investment wave >

India's semiconductor push is bearing fruit with Rs1.56tr worth of investments approved and underway. This includes 70% fiscal support from central and state governments. These include India's first chip fabrication plant, multiple ATMP plants and over 80 startup-led design initiatives.

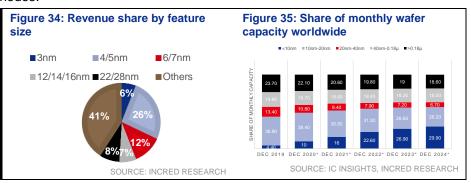

The first semiconductor chip fabrication plant will manufacture chips ranging from 28-110nm. The latest of this, the 28nm technology was launched in 2011. While this investment of Rs910bn in a 14-year+ old technology might seem outdated compared to a 2nm or 5nm fab, it serves as a strategic investment to kickstart the semiconductor ecosystem. Mature nodes (28nm+) still account for ~40% of global installed capacity and revenue. Moreover, the cost of setting up a single fab can range between US\$5bn to US\$20bn depending on the size, technology and location, with advanced node fab requiring a much higher capex than mature nodes.

In the initial semiconductor fab scheme of the government, the government tried to incentivize advanced chip fabrication more than mature node fabrication but that scheme failed to gain traction from the private players to invest. The government's focus on this industry has since evolved towards a more pragmatic phased approach, prioritizing mature node fabs, ATMP/OSAT facilities, and semiconductor design initiatives as the first step. This shift aims to build foundational capabilities, strengthen the domestic ecosystem, and gradually move towards advanced node manufacturing over time.

• Tata Electronics and PSMC Semiconductor Fab -

Tata Electronics was established in 2020 as a greenfield venture of the Tata Group with fast emerging capabilities in electronics manufacturing services (EMS), semiconductor assembly and test, semiconductor foundry and design services. Powerhouse Semiconductor Manufacturing Service (PSMC) is a Taiwanese company that has a major global semiconductor foundry (ninth biggest by revenue), known for its expertise in advanced memory and logic chips.

This fab is set to open in 2026F in Dholera and will have manufacturing capacity of up to 50,000 wafers per month. The new semiconductor fab will manufacture chips for applications such as power management IC, display drivers, microcontrollers (MCU) and high-performance computing logic on 28-110nm technologies, addressing the rising demand in markets such as computing,

communication, automotive, IoT and data storage. The total investment in this project is up to Rs915.26bn, of which the company will bear 30% of the cost, the central government will bear 50% and the Gujarat will bear 20% of the cost.

• Tata Electronics OSAT facility -

This is the second facility being set up by Tata Electronics to expand its presence in the semiconductor value chain. This state-of-the-art, greenfield semiconductor assembly and test facility will be set up at Jagiroad in Assam at a cost of Rs270bn. This facility is designed to produce up to 48m chips per day using advanced packaging technologies like Wire Bond, Flip Chip, and a differentiated offering called Integrated Systems Packaging (ISP), with plans of expanding the roadmap to advanced packaging technologies in the future.

This facility is expected to start operations in mid-2025F and the reason for this location stems from factors like the Government of India's northeastern push, and proximity to fast-growing emerging ASEAN market.

• Micron's ATMP facility -

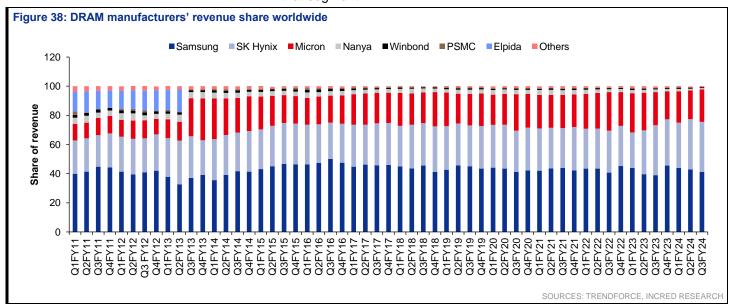

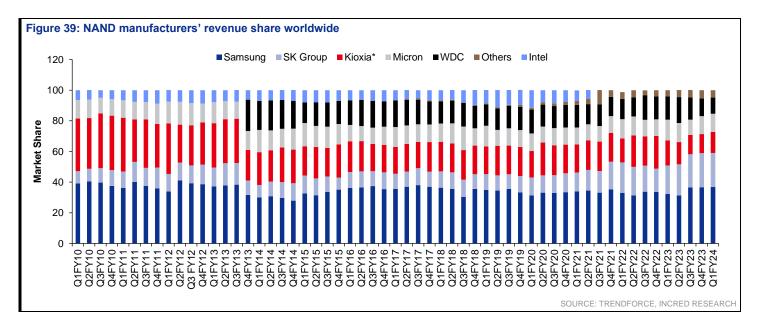

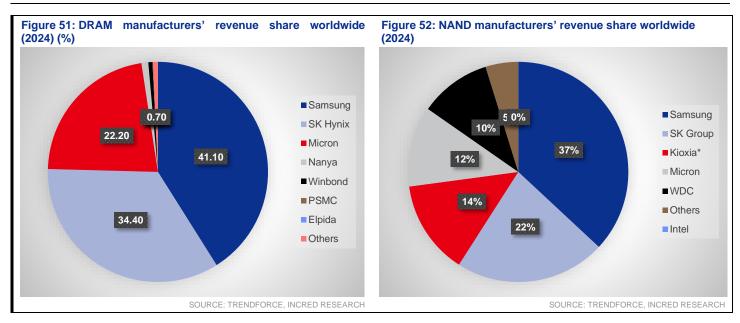

Micron Technology is a US-based global leader in memory (DRAM and NAND) chips. It is the fourth-largest NAND Flash manufacturer worldwide by revenue and holds a 11.8% market share in that segment and it is also the third largest DRAM manufacturer worldwide by revenue and holds a 22.2% market share in that segment.

It announced a Rs270bn investment for an ATMP facility at Sanand in Gujarat. Micron's new facility will focus on transforming wafers into ball grid array (BGA) integrated circuit packages, memory modules and solid-state drives. It will cater to data centres, smartphones and IoT devices.

CG Power, Renesas and Stars Microelectronics –

CG Power and Industrial Solutions is a major player in the electrical engineering industry and offers a diverse range of products in its two business lines - industrial systems and power systems. Since Nov 2020, the company has become a part of the renowned Murugappa Group. Renesas Electronics, based in Tokyo, is a prominent player in microcontrollers and System on Chip (SoC) solutions. It is a global leader in the automotive semiconductor market. Stars Microelectronics, located in Thailand, is a total electronic solutions provider to Outsource Semiconductor Assembly and Test (OSAT) and electronics manufacturing services (EMS).

CG Power and Industrial Solutions is setting up its semiconductor OSAT unit at Sanand in Gujarat, which is in partnership with Renesas Electronics America Inc. and Stars Microelectronics (Thailand) Public Co. with a total investment of approximately Rs76bn. The JV will be 92.3% owned by CG, with Renesas and Stars Microelectronics each holding equity capital of approximately 6.8% and 0.9%, respectively. The JV will manufacture a wide range of products – ranging from legacy packages such as QFN and QFP to advanced packages such as FC BGA, and FC CSP. The JV will cater to industries such as automotive, consumer, industrial, 5G, to name a few.

• Kaynes Semicon –

Kaynes Technology is a leading end-to-end and IoT solutions-enabled integrated electronics manufacturer in India with capabilities across the entire spectrum of ESDM services. In 2023, Kaynes ventured into the semiconductor domain by establishing a wholly-owned subsidiary, Kaynes Semicon Pvt. Ltd., focusing on OSAT services.

The company received approval under the ISM to set up a state-of-the-art OSAT facility at Sanand in Gujarat with an investment of Rs33bn. This facility will produce chips that will cater to a wide variety of applications which include segments such as industrial, automotive, electric vehicle, consumer electronics, telecom, mobile phone, etc.

• Other emerging players in India's semiconductor ecosystem -

Apart from ISM-supported projects, companies like Sahasra Semiconductors and Suchi Semiconductors are also contributing to India's semiconductor manufacturing ecosystem through other government schemes. Sahasra Semiconductors has set up an ATMP facility for memory chip packaging at Bhiwadi in Rajasthan, with an investment of approximately Rs7.5bn, focusing on DRAM modules, SSDs, and embedded solutions. Suchi Semiconductors is establishing an OSAT (Outsourced Semiconductor Assembly and Test) facility at Surat in Gujarat, with a planned investment of around Rs8.7bn, aiming to serve sectors like automotive, consumer electronics, and industrial electronics. Importantly, both Sahasra and Suchi have not availed subsidies under the India Semiconductor Mission (ISM) but have leveraged benefits under SPECS and state-level incentive programs.

| Figure 40:                                                    |                  |                          |                                    |                                  |                      |

|---------------------------------------------------------------|------------------|--------------------------|------------------------------------|----------------------------------|----------------------|

| Project                                                       | Location         | Total Capex<br>(in Rs m) | Central<br>Government<br>(in Rs m) | State<br>Government<br>(in Rs m) | Company<br>(in Rs m) |

| Tata Electronics and PSMC<br>Semiconductor fab                | Dholera, Gujarat | 9,15,260                 | 4,57,630                           | 1,83,052                         | 2,74,578             |

| Tata Electronics OSAT facility                                | Jagiroad, Assam  | 2,70,000                 | 1,35,000                           | 54,000                           | 81,000               |

| Micron's ATMP facility                                        | Sanand, Gujarat  | 2,70,000                 | 1,35,000                           | 54,000                           | 81,000               |

| CG Power, Renesas and Stars<br>Microelectronics OSAT facility | Sanand, Gujarat  | 76,000                   | 38,000                             | 15,200                           | 22,800               |

| Kaynes Semicon OSAT facility                                  | Sanand, Gujarat  | 33,000                   | 16,500                             | 6,600                            | 9,900                |

|                                                               | Total            | 15,64,260                | 7,82,130                           | 3,12,852                         | 4,69,278             |